PCIe

Overview

Product Versions

| Chip Name | Kernel Version |

|---|---|

| RK1808 | 4.4, 4.19 |

| RK3528 | 4.19, 5.10, 6.1 |

| RK3562 | 5.10, 6.1 |

| RK3566/RK3568 | 4.19, 5.10, 6.1 |

| RK3576 | 6.1 |

| RK3588 | 5.4, 5.10, 6.1 |

Note: RK3399 uses a different PCIe controller IP and is not covered in this document. Please refer to "Rockchip_RK3399_Developer_Guide_PCIe_CN".

Target Audience

This document (guide) is mainly intended for the following engineers:

- Technical Support Engineers

- Software Development Engineers

1. Chip Resource Introduction

1.1 RK1808

| Resource | Mode | Supported Lanes | DMA Support | MMU Support | ASPM Support | Remarks |

|---|---|---|---|---|---|---|

| PCIe Gen2 | RC | x2 lane | No | No | L0s/L1 | Internal clock |

1.2 RK3528

| Resource | Mode | Lane Split Support | DMA Support | MMU Support | ASPM Support | Remarks |

|---|---|---|---|---|---|---|

| PCIe Gen2 x1 | RC | No | No | No | ALL | Internal clock |

1.3 RK3562

| Resource | Mode | Lane Split Support | DMA Support | MMU Support | ASPM Support | Remarks |

|---|---|---|---|---|---|---|

| PCIe Gen2 x1 | RC | No | No | No | ALL | Internal clock |

1.4 RK3566

| Resource | Mode | Lane Split Support | DMA Support | MMU Support | ASPM Support | Remarks |

|---|---|---|---|---|---|---|

| PCIe Gen2 x1 | RC | No | No | No | L0s/L1 | Internal clock |

1.5 RK3568

1.5.1 Controller

| Resource | Mode | Lane Split | DMA Support | MMU Support | ASPM Support | Remarks |

|---|---|---|---|---|---|---|

| PCIe Gen2 | RC | 1 lane only | No | No | L0s/L1 | Internal clock |

| PCIe Gen3 | RC/EP | 1 lane RC + 1 lane RC | 2 read Channels + 2 write Channels | No | ALL | Supports pcie30phy |

| PCIe Gen3 | RC | 1 lane | No | No | ALL | Supports pcie30phy |

1.5.2 PHY

| Resource | dts Node | Reference Clock | Split | Combo |

|---|---|---|---|---|

| pcie30phy | phy@fe8c0000 | External | 2Lane: Default | PCIe dedicated |

| combphy2_psq | phy@fe840000 | Internal/External | 1Lane + 1Lane: rockchip,bifurcation | combo |

Note: pcie30phy 2Lane is by default configured as PCIe Gen3 x 2 lane. After splitting, the "PCIe Gen3 x 2 lane" and "PCIe Gen3 x 1 lane" controllers each use 1 lane.

1.6 RK3576

| Resource | Mode | Lane Split Support | DMA Support | MMU Support | ASPM Support | Remarks |

|---|---|---|---|---|---|---|

| PCIe Gen2 x1 | RC | No | No | Yes | ALL | Internal clock |

1.7 RK3588

Note: RK3588 has a total of 5 PCIe controllers, with identical hardware IP but different configurations. One 4Lane DM mode can support EP usage, while the other 2Lane and three 1Lane controllers can only be used as RC. RK3588 has two types of PCIe PHY: one is pcie3.0PHY with 2 Ports and 4 Lanes; the other is pcie2.0 PHY, each being 2.0 1Lane, used in combo with SATA and USB. The 4Lane of pcie3.0 PHY can be split as needed. After splitting, the corresponding controllers must be properly configured. All configurations are done in DTS, no driver modification required.

Usage restrictions:

- After splitting pcie30phy, the pcie30x4 controller, when working in 2Lane mode, can only be paired with port0 of pcie30phy; in 1Lane mode, it can only be paired with port0lane0 of pcie30phy;

- After splitting pcie30phy, the pcie30x2 controller, when working in 2Lane mode, can only be paired with port1 of pcie30phy; in 1Lane mode, it can only be paired with port1lane0 of pcie30phy;

- When pcie30phy is split into four 1Lanes, port0lane1 of pcie3phy can only be paired with the pcie2x1l0 controller, and port1lane1 of pcie3phy can only be paired with the pcie2x1l1 controller;

- The pcie30x4 controller working in EP mode can use 4Lane mode, or use 2Lane mode with port0 of pcie30phy. The 2Lane of port1 of pcie30phy can be used as RC with other controllers. By default, when using common clock as the reference clock, it is not possible to have lane0 of port0 of pcie30phy working in EP mode and lane1 working in RC mode with other controllers, because the two lanes of port0 share one input reference clock, and simultaneous use of clock by RC and EP may cause conflicts.

- If only one port of RK3588 pcie30phy is used, the other port also needs to be powered, and other signals such as refclk can be grounded.

1.7.1 Controller

| Resource | Mode | dts Node | Available PHY | Internal DMA | ASPM Support | MMU Support |

|---|---|---|---|---|---|---|

| PCIe Gen3 x4 | RC/EP | pcie3x4: pcie@fe150000 | pcie30phy | 2 read Channels + 2 write Channels | ALL | Yes |

| PCIe Gen3 x2 | RC | pcie3x2: pcie@fe160000 | pcie30phy | No | ALL | Yes |

| PCIe Gen3 x1 | RC | pcie2x1l0: pcie@fe170000 | pcie30phy, combphy1_ps | No | ALL | Yes |

| PCIe Gen3 x1 | RC | pcie2x1l1: pcie@fe180000 | pcie30phy, combphy2_psu | No | ALL | Yes |

| PCIe Gen3 x1 | RC | pcie2x1l2: pcie@fe190000 | combphy0_ps | No | ALL | Yes |

1.7.2 PHY

| Resource | dts Node | Reference Clock | Split | Combo |

|---|---|---|---|---|

| pcie30phy | phy@fee80000 | External | 4Lane: PHY_MODE_PCIE_AGGREGATION 2Lane+2Lane: PHY_MODE_PCIE_NANBNB 2Lane+1Lane+1Lane: PHY_MODE_PCIE_NANBBI 1Lane4: PHY_MODE_PCIE_NABIBI | PCIe dedicated |

| combphy0_ps | phy@fee00000 | Internal/External | - | Combo with SATA |

| combphy1_ps | phy@fee10000 | Internal/External | - | Combo with SATA |

| combphy2_psu | phy@fee20000 | Internal/External | - | Combo with SATA/USB3 |

1.8 RK3588S

Note: The PCIe of RK3588S is relatively simple, with two 1Lane controllers and two 1Lane comboPHYs for PCIe 2.0, in a one-to-one correspondence.

1.8.1 Controller

| Resource | Mode | dts Node | Available PHY | Internal DMA | ASPM Support | MMU Support |

|---|---|---|---|---|---|---|

| PCIe Gen3 x1 | RC | pcie2x1l1: pcie@fe180000 | combphy2_psu | No | ALL | Yes |

| PCIe Gen3 x1 | RC | pcie2x1l2: pcie@fe190000 | combphy0_ps | No | ALL | Yes |

1.8.2 PHY

| Resource | dts Node | Reference Clock | Split | Combo |

|---|---|---|---|---|

| combphy0_ps | phy@fee00000 | Internal/External | - | Combo with SATA |

| combphy2_psu | phy@fee20000 | Internal/External | - | Combo with SATA/USB3 |

2. DTS Configuration

2.1 Key Points for Configuration��

Most PCIe configurations are fixed, and there are not many variables that need to be configured in the board-level dts. Refer to the following key points for configuration:

- Controller/PHY Enable: Enable the correct controller and PHY according to the schematic. Note that the index of the controller and the index of the phy may not match sequentially.

- Controller: Some controllers (such as RK3588's pcie2x1l0 and pcie2x1l1) have multiple PHYs to choose from. Configure "phys" correctly according to the design.

- Controller: As RC, usually need to configure "reset-gpios", corresponding to the "PERSTn" signal of PCIe in the schematic.

- Controller: As RC, may need to configure "vpcie3v3-supply", corresponding to the fixed regulator controlled by the "PWREN" gpio signal of PCIe.

- Controller: When used as EP, need to modify "compatible" to the corresponding string for EP mode.

- PHY: pcie30phy has 4 lanes and can be split. Configure the "rockchip,pcie30-phymode" mode correctly according to the design.

2.2 RK1808 DTS Configuration

For RK1808 dts configuration, all implementation modes have examples in the SDK evb code. You can select the matching content from the table below and copy it to the product board-level dts for use.

| Resource | Mode | Reference Configuration | Controller Node | PHY Node | Remarks |

|---|---|---|---|---|---|

| PCIe Gen2 x2 lane | RC | rk1808-evb.dtsi | pcie0 | combphy | Need to disable usbdrd_dwc3 and usbdrd3 |

| PCIe Gen2 x2 lane | EP | Add compatible = "rockchip,rk1808-pcie-ep","snps,dw-pcie"; to the pcie0 node in rk1808-evb.dtsi | pcie0 | combphy | Need to disable usbdrd_dwc3 and usbdrd3 |

2.3 RK3528 DTS Configuration

For RK3528 dts configuration, all implementation modes have examples in the SDK evb code. You can select the matching content from the table below and copy it to the product board-level dts for use.

| Resource | Mode | Reference Configuration | Controller Node | PHY Node |

|---|---|---|---|---|

| PCIe Gen2 x1 lane | RC | rk3528-evb2-ddr3-v10.dtsi | pcie2x1 | combphy_pu |

2.4 RK356X DTS Configuration

For RK356x dts configuration, all implementation modes have examples in the SDK evb code. You can select the matching content from the table below and copy it to the product board-level dts for use.

2.4.1 RK3562 dts

| Resource | Mode | Reference Configuration | Controller Node | PHY Node |

|---|---|---|---|---|

| PCIe Gen2 x1 lane | RC | rk3562-evb1-lp4x-v10.dtsi | pcie2x1 | combphy_pu |

2.4.2 RK3566 dts

| Resource | Mode | Reference Configuration | Controller Node | PHY Node |

|---|---|---|---|---|

| PCIe Gen2 x1 lane | RC | rk3566-evb1-ddr4-v10.dtsi | pcie2x1 | combphy2_psq |

2.4.3 RK3568 dts

| Resource | Mode | Reference Configuration | Controller Node | PHY Node |

|---|---|---|---|---|

| PCIe Gen2 x1 lane | RC | rk3568-evb2-lp4x-v10.dtsi | pcie2x1 | combphy2_psq |

| PCIe Gen3 x2 lane | RC | rk3568-evb1-ddr4-v10.dtsi | pcie3x2 | pcie30phy |

| PCIe Gen3 split 1 lane | RC | rk3568-evb6-ddr3-v10.dtsi | pcie3x2 | pcie30phy pcie3x1 |

| PCIe Gen3 x2 lane | EP | rk3568-iotest-ddr3-v10.dts | pcie3x2 | pcie30phy |

2.4.4 RK3576 dts

| Resource | Mode | Reference Configuration | Controller Node | PHY Node |

|---|---|---|---|---|

| PCIe Gen2 x1 lane | RC | rk3576-test1.dtsi | pcie0 | combphy0_ps |

| PCIe Gen2 x1 lane | RC | rk3576-test1.dtsi | pcie1 | combphy1_psu |

2.5 RK3588 DTS Configuration

RK3588 has many controllers and PHYs, so it is not possible to enumerate all combinations in the SDK evb code. Just configure according to the key points. Here are some typical examples for reference.

2.5.1 Example 1: pcie3.0 4Lane RC + 2 pcie 2.0 (comboPHY) (RK3588 evb1)

/ {

vcc3v3_pcie30: vcc3v3-pcie30 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_pcie30";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

enable-active-high;

gpios = <&gpio3 RK_PC3 GPIO_ACTIVE_HIGH>;

startup-delay-us = <5000>;

vin-supply = <&vcc12v_dcin>;

};

};

&combphy1_ps {

status = "okay";

};

&combphy2_psu {

status = "okay";

};

&pcie2x1l0 {

phys = <&combphy1_ps PHY_TYPE_PCIE>;

reset-gpios = <&gpio4 RK_PA5 GPIO_ACTIVE_HIGH>;

status = "okay";

};

&pcie2x1l1 {

phys = <&combphy2_psu PHY_TYPE_PCIE>;

reset-gpios = <&gpio4 RK_PA2 GPIO_ACTIVE_HIGH>;

pinctrl-names = "default";

pinctrl-0 = <&rtl8111_isolate>;

status = "okay";

};

&pcie30phy {

rockchip,pcie30-phymode = <PHY_MODE_PCIE_AGGREGATION>;

status = "okay";

};

&pcie3x4 {

reset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

2.5.2 Example 2: pcie3.0phy split into two 2Lane RC, three PCIe 2.0 1Lane (comboPHY)

/ {

vcc3v3_pcie30: vcc3v3-pcie30 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_pcie30";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

enable-active-high;

gpios = <&gpio3 RK_PC3 GPIO_ACTIVE_HIGH>;

startup-delay-us = <5000>;

vin-supply = <&vcc12v_dcin>;

};

};

&combphy0_ps {

status = "okay";

};

&combphy1_ps {

status = "okay";

};

&combphy2_psu {

status = "okay";

};

&pcie2x1l0 {

phys = <&combphy1_ps PHY_TYPE_PCIE>;

reset-gpios = <&gpio4 RK_PA5 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie2x1l1 {

phys = <&combphy2_psu PHY_TYPE_PCIE>;

reset-gpios = <&gpio4 RK_PA2 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie2x1l2 {

reset-gpios = <&gpio4 RK_PC1 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie30phy {

rockchip,pcie30-phymode = <PHY_MODE_PCIE_NANBNB>;

status = "okay";

};

&pcie3x2 {

reset-gpios = <&gpio4 RK_PB0 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie3x4 {

num-lanes = <2>;

reset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

2.5.3 Example 3: pcie3.0phy split into four 1Lane, one uses PCIe 2.0 1 Lane (comboPHY)

Note

pcie2x1l0/pcie2x1l1are connected to the correspondingTX/RXsignals ofpcie3.0phyin hardware, so disable thecombphy1_ps/combphy2_psunodes in dts.

Reference code

/ {

vcc3v3_pcie30: vcc3v3-pcie30 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_pcie30";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

enable-active-high;

gpios = <&gpio3 RK_PC3 GPIO_ACTIVE_HIGH>;

startup-delay-us = <5000>;

vin-supply = <&vcc12v_dcin>;

};

};

&combphy0_ps {

status = "okay";

};

&pcie2x1l0 {

phys = <&pcie30phy>;

reset-gpios = <&gpio4 RK_PA5 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie2x1l1 {

phys = <&pcie30phy>;

reset-gpios = <&gpio4 RK_PA2 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie2x1l2 {

reset-gpios = <&gpio4 RK_PC1 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie30phy {

rockchip,pcie30-phymode = <PHY_MODE_PCIE_NABIBI>;

status = "okay";

};

&pcie3x2 {

num-lanes = <1>;

reset-gpios = <&gpio4 RK_PB0 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

&pcie3x4 {

num-lanes = <1>;

reset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

2.6 DTS Property Description

2.6.1 Common Controller DTS Configurations

-

compatible

- Optional: Set whether the PCIe interface uses RC mode or EP mode.

- RK3568 as RC:

compatible = "rockchip,rk3568-pcie", "snps,dw-pcie"; - RK3568 as EP:

compatible = "rockchip,rk3568-pcie-ep", "snps,dw-pcie"; - For RK1808, RK3588: replace

rk3568withrk1808andrk3588respectively.

- RK3568 as RC:

- Optional: Set whether the PCIe interface uses RC mode or EP mode.

-

reset-gpios

- Required: Set the

PERST#reset signal for the PCIe interface.- Example:

reset-gpios = <&gpio3 13 GPIO_ACTIVE_HIGH>; - Note: If multiple lane PCIe interfaces are split, each node needs to configure a different

PERST#signal line.

- Example:

- Required: Set the

-

num-lanes

- Optional: Set the number of lanes used by the PCIe device.

- Example:

num-lanes = <4>; - The default configuration is in the chip-level dtsi. It is recommended to configure according to the actual hardware.

- Example:

- Optional: Set the number of lanes used by the PCIe device.

-

max-link-speed

- Optional: Set the PCIe bandwidth version.

- 1 means Gen1, 2 means Gen2, 3 means Gen3.

- Example:

max-link-speed = <2>; - In principle, it does not need to be configured for every board, only for testing or downgrade purposes.

- Optional: Set the PCIe bandwidth version.

-

status

- Required: Enable both the PCIe controller node and the corresponding phy node.

- Example:

status = "okay";

- Example:

- Required: Enable both the PCIe controller node and the corresponding phy node.

-

vpcie3v3-supply

- Optional: Used to configure the 3V3 power supply for PCIe peripherals (in principle, our hardware reference schematic merges the 12V and 3V3 power supplies of the PCIe slot, so after configuring the 3v3 power supply, the 12V power supply is also controlled together). If the 3V3 for PCIe peripherals needs to be controlled on the board, define a corresponding regulator as shown in the example. For regulator configuration, refer to Documentation/devicetree/bindings/regulator/. Also, if it is a PCIe3.0 controller, an external 100M crystal oscillator chip is generally required. The power supply for this crystal oscillator chip is usually shared with the 3V3 for PCIe peripherals in hardware design. Therefore, after configuring this item, in addition to confirming the 3V3 power supply for peripherals, also confirm whether the external crystal oscillator chip outputs the clock normally. Generally, the external crystal oscillator chip requires a stable period to output the clock. Please strictly refer to the minimum value specified in the clock chip manual, and specify the value of startup-delay-us in the power node with a test margin. For hardware designs with slow discharge after power off, specify the value of off-on-delay-us in the power node to ensure sufficient power cycling. For details, refer to the vcc3v3_pcie node in the rk3568-evb1-ddr4-v10.dtsi file.

-

phys

- Optional: Used to configure the phandle reference of the phy used by the controller. Some controllers can be routed to multiple phys (such as RK3588's pcie2x1l0 and pcie2x1l1). Note that different phys may have different reference methods. comboPHY needs to specify the working mode of the phy at the same time, as follows:

- Example:

phys = <&pcie30phy>;

phys = <&combphy1_ps PHY_TYPE_PCIE>;

- Example:

- Optional: Used to configure the phandle reference of the phy used by the controller. Some controllers can be routed to multiple phys (such as RK3588's pcie2x1l0 and pcie2x1l1). Note that different phys may have different reference methods. comboPHY needs to specify the working mode of the phy at the same time, as follows:

-

rockchip,bifurcation

- Optional: This is a special configuration for the RK3568 chip. It can split the two lanes of pcie3x2 into two 1-lane controllers. The specific configuration method is to enable both the pcie3x1 and pcie3x2 controller nodes and the pcie30phy in dts, and add the rockchip,bifurcation property to both the pcie3x2 and pcie3x1 nodes. Refer to rk3568-evb6-ddr3-v10.dtsi. Otherwise, by default, the pcie3x1 controller cannot be used.

At this time, lane0 is used by the pcie3x2 controller, and lane1 is used by the pcie3x1 controller. The hardware layout strictly follows our schematic. Also note that in this mode, both 1-lane controllers must work in RC mode.

Also pay special attention: after PCIe 3.0 is split into two single lanes and connected to two different peripherals, since the crystal oscillator and its power supply are controlled by the same circuit, do not configure vpcie3v3-supply for only one controller. Otherwise, the controller that obtains the 3v3 voltage operation permission will interfere with the normal initialization of the peripheral connected to the other controller. In this case, the regulator corresponding to vpcie3v3-supply should be configured as regulator-boot-on and regulator-always-on.

-

prsnt-gpios = <&gpio4 15 GPIO_ACTIVE_LOW>;

- Optional configuration: Used for the driver to detect the presence of peripherals and related circuits. If a valid level is detected, the device detection process is skipped. According to the PCIe electrical specification, this GPIO being low indicates a device is present. If your board design is the opposite, you can change it to GPIO_ACTIVE_HIGH to indicate high level means device present. This signal allows the same software to support both products with and without PCIe3 on the same board type, avoiding system exceptions such as rcu stall during PCIe controller initialization.

rockchip,perst-inactive-ms = <500>;

- Optional configuration: Used to configure the reset time of the device #PERST reset signal, in milliseconds. According to the PCIe Express Card Electromechanical Spec, the minimum requirement from downstream device power stable to #PERST release is 100ms. If not configured, the RK driver defaults to 200ms. If this still does not meet the peripheral's requirements, you can adjust as needed based on actual testing.

rockchip,s2r-perst-inactive-ms = <1>;

- Optional configuration: Used to configure the reset time of the device #PERST signal during suspend/resume, in milliseconds. If not configured, its value is the same as rockchip,perst-inactive-ms. If the peripheral is not powered off during suspend, such as Wi-Fi, then #PERST remains in reset during suspend, so the reset time during resume can be shortened, even set to 0.

rockchip,wait-for-link-ms = <1>;

- Optional configuration: Used to configure the wait time after releasing the device #PERST reset signal, in milliseconds. This is for peripherals that require a longer internal initialization time, to prevent system link timeout due to slow initialization. Common devices needing this are FPGAs and some AI accelerator cards.

- supports-clkreq

- Optional configuration: Only valid in RC mode. Please ensure the CLKREQ# pinctrl iomux is set to function io. If this property exists, it indicates that there is a CLKREQ# signal route from the root port to the downstream device, and the host bridge driver can program accordingly. For example, if there is no CLKREQ# signal, the root port will be set to not support PM L1 Substates.

- rockchip,lpbk-master

- Special debug configuration: This is for loopback signal testing, using the PCIe controller to simulate a loopback master environment, letting the device under test enter slave mode. Do not configure this unless you are doing simulation lab RX loopback tests. Note that Gen3 controllers may require compliance mode for loopback slave mode. If you do not understand loopback testing, this is not the configuration you are looking for, do not ask about it.

- rockchip,compliance-mode

- Special debug configuration: This is for compliance signal testing, forcing the PCIe controller into compliance test mode or keeping it powered on after entering test mode with an SMA fixture. This is an array with two values: the first is the test mode, the second is the preset value for that mode. If using an SMA fixture, configure

rockchip,compliance-mode=<0 0>;. If testing soldered devices, fix the mode and preset values,rockchip,compliance-mode=<mode preset>;. Mode can be 1, 2, or 3, representing 2.5GT, 5.0GT, and 8GT signals. Only in 5GT and 8GT modes, preset values 0-10 are valid, representing P0-P10 protocol pre-emphasis settings. See the appendix "PCIe TX Pre-emphasis Preset Table" for details.

- rockchip,keep-power-in-suspend

- Optional configuration: Only valid in RC mode. Used to keep the peripheral powered and reset during suspend. Allows the peripheral to work offline after system suspend. This mode also requires the pcie node to reference

vpcie3v3-supply.

2.6.2 comboPHY dts configuration

- The following configurations do not apply to the combphy node of RK1808.

- The number in the

combphynode indicates the Mux relationship, and the suffix indicates the multiplexing relationship:p,s,u,qrepresent PCIe, SATA, USB, QSGMII respectively.

- rockchip,ext-refclk

-

Special debug configuration: Note this is only for combophy. By default, combophy uses the SoC internal clock. For example, in RK356X, see the rk3568.dtsi node, which uses a 24MHz clock source by default. Besides 24MHz, 25M and 100M are also supported, just set

assigned-clock-rates = <24000000>to the desired frequency. The internal clock is the most cost-effective and is the SDK default, but combophy still reserves the option for an external crystal oscillator. If you need to use an external oscillator, add rockchip,ext-refclk to the combphy node used by the PCIe controller in the board dts, and setassigned-clock-rates = <frequency>to specify the external oscillator frequency, still only supporting 24M, 25M, 100M.- rockchip,enable-ssc

- Special debug configuration: Only for the combphy node used by PCIe. By default, combophy output clock does not enable spread spectrum. If you need to mitigate EMI issues, add this property to the corresponding combphy node to enable SSC.

2.6.3 pcie30phy dts configuration

- rockchip,pcie30-phymode

- Optional configuration: This configures the pcie30phy combination mode, which must be set correctly. Default is 4Lane shared. For details, see

include/dt-bindings/phy/phy-snps-pcie3.h:

- Optional configuration: This configures the pcie30phy combination mode, which must be set correctly. Default is 4Lane shared. For details, see

/*

* pcie30_phy_mode[2:0]

* bit2: aggregation

* bit1: bifurcation for port 1

* bit0: bifurcation for port 0

*/

#define PHY_MODE_PCIE_AGGREGATION 4 /* PCIe3x4 */

#define PHY_MODE_PCIE_NANBNB 0 /* P1:PCIe3x2 + P0:PCIe3x2 */

#define PHY_MODE_PCIE_NANBBI 1 /* P1:PCIe3x2 + P0:PCIe3x1*2 */

#define PHY_MODE_PCIE_NABINB 2 /* P1:PCIe3x1*2 + P0:PCIe3x2 */

#define PHY_MODE_PCIE_NABIBI 3 /* P1:PCIe3x1*2 + P0:PCIe3x1*2 */

2.7 Fill in DTS according to schematic

2.7.1 Low-speed IO description

PCIe module chip signal connections, besides data lines and reference clock differential pairs, may also have the following low-speed IOs:

IO Name RC Mode EP Mode Description PERSTn GPIO output Connect nPOR Required, configure dts "reset-gpios"WAKE GPIO (PMU domain) GPIO output Optional, function driver registers GPIO interrupt and wake source, not handled by PCIe controller driver PWREN GPIO output None Optional, configure dts "vpcie3v3-supply"CLKREQ FUNCTION FUNCTION Optional, used for L1SS, configure dts "supports-clkreq"PRSNT GPIO input None Optional, configure dts "prsnt-gpios"- Only

CLKREQuses PCIe function; this signal is only needed for L1SS. Otherwise, it can be left unconnected. If used, the corresponding dts property must be added. - Other signals use GPIO function; do not configure them as PCIe function in pinctrl. See dts configuration instructions for details.

- The

PERSTsignal is required by the protocol; other signals are configured as needed for the project.

2.7.2 DTS configuration method

The schematic describes hardware from the IO signal perspective, and IO signals are strongly related to PHY index, but the controller and PHY index of RK3588 may not match, so pay special attention when reading the schematic.

Recommended steps for filling in dts based on the hardware schematic:

- Confirm PCIe device allocation:

- Confirm with hardware engineers how many PCIe devices are used and how the chip's PCIe interfaces are allocated.

- Find PHY output:

- In the schematic, find which PHY output the PCIe data lines for each device use.

- Determine controller and PHY:

- Determine which controller and PHY each device uses, and enable them in dts.

- Check controller

phyproperty:- Ensure the controller dts

"phy"property and mode are correct, e.g.,pcie2x1lncontroller should usecomboPHYand specifyPHY_TYPE_PCIE.

- Ensure the controller dts

- Disable other controllers:

- If

comboPHYmay be shared bySATA,USB,RGMII, etc., ensure other controllers are disabled in dts.

- If

- Configure PHY mode:

- Ensure the PHY has the correct working mode, e.g., pcie30phy split combinations must be configured correctly.

- Configure

PERSTnsignal:- Ensure the correct GPIO for

PERSTnis configured in the controller dts node.

- Ensure the correct GPIO for

- Configure

PWRENsignal:- Ensure the correct GPIO for

PWRENis configured in the controller dts node (or in the onboard peripheral dts).

- Ensure the correct GPIO for

- Configure other peripheral hardware:

- Configure other hardware required for the peripheral.

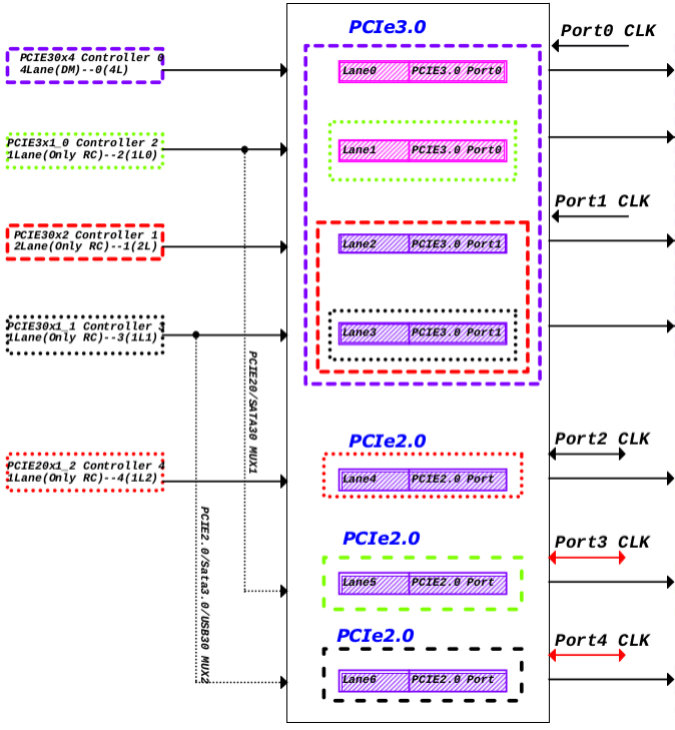

The following diagram shows RK3588 pcie30phy and its possible controllers. Red boxes are controllers, pink boxes are PHY signals, green boxes are peripheral signals. Which controller is used can be confirmed by peripheral signal connections or by checking with hardware engineers. This diagram is from RK3588 evb1, with a PCIe3.0 x4 slot connected, so the controller used is PCIe30X4 (dts name pcie3x4), and other controllers are not used with this PHY.

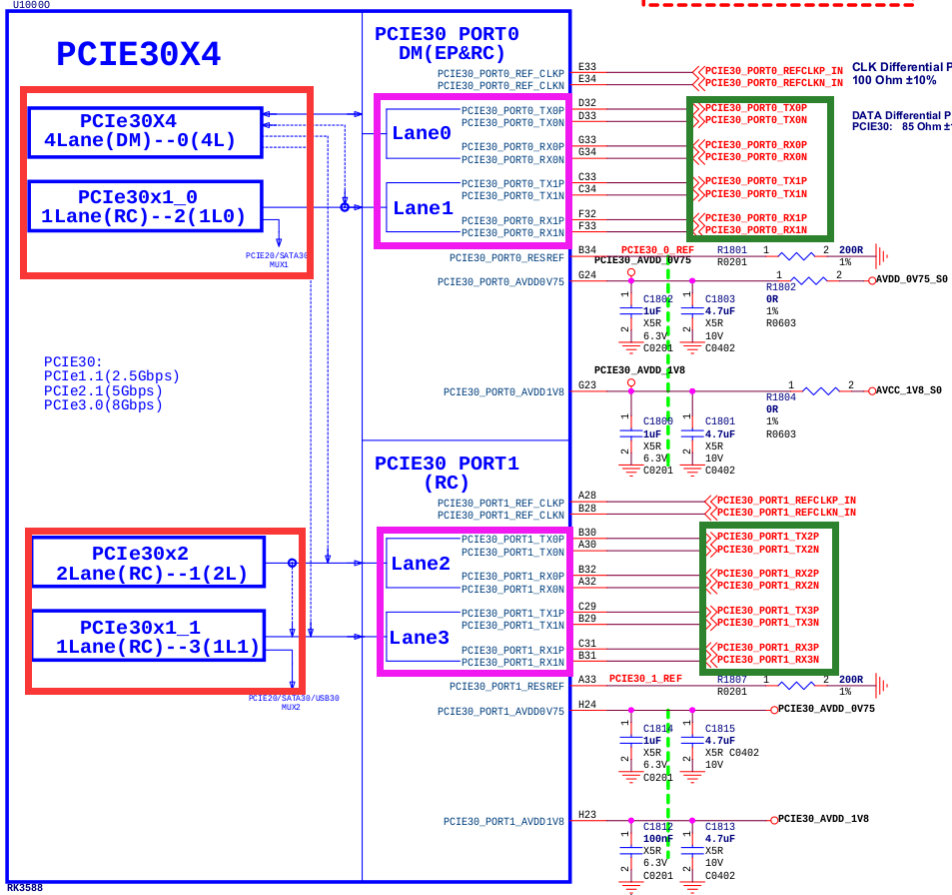

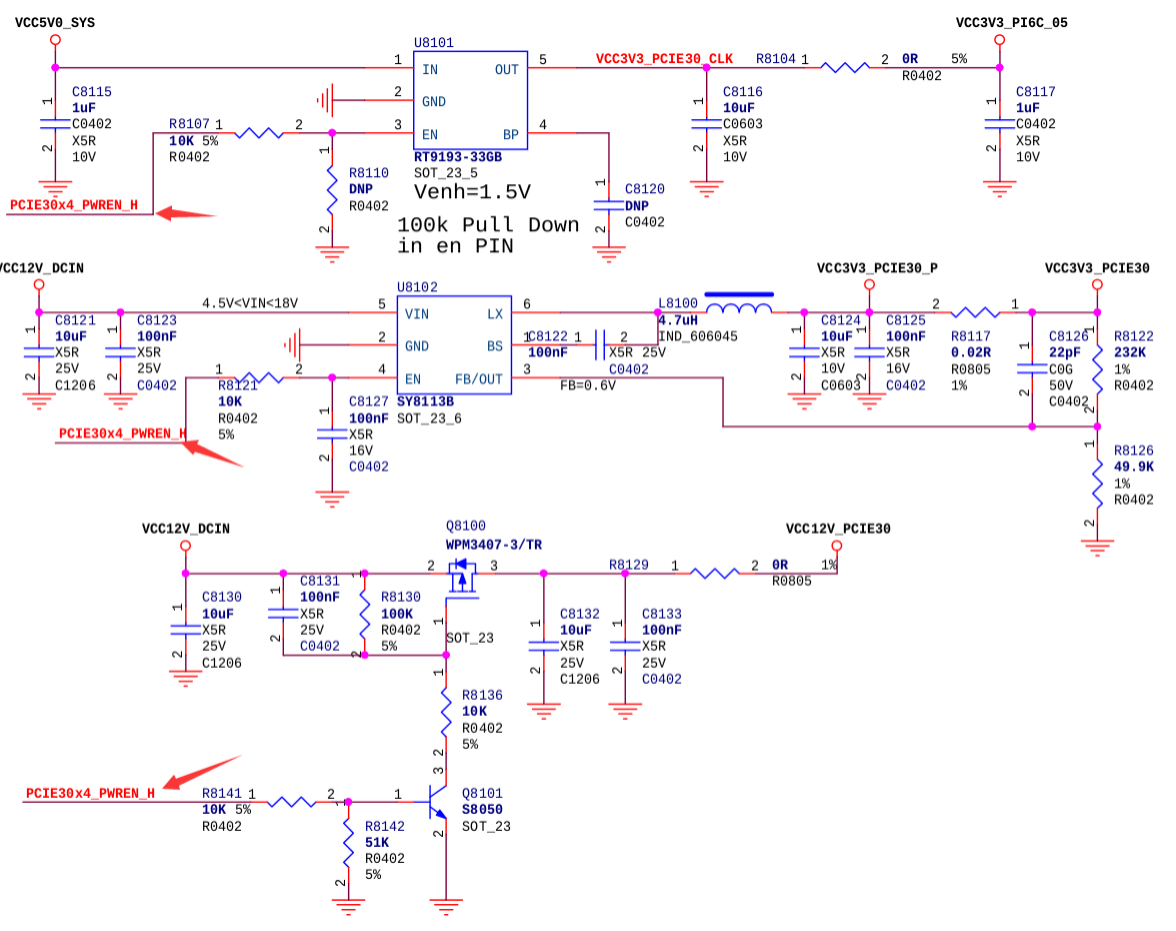

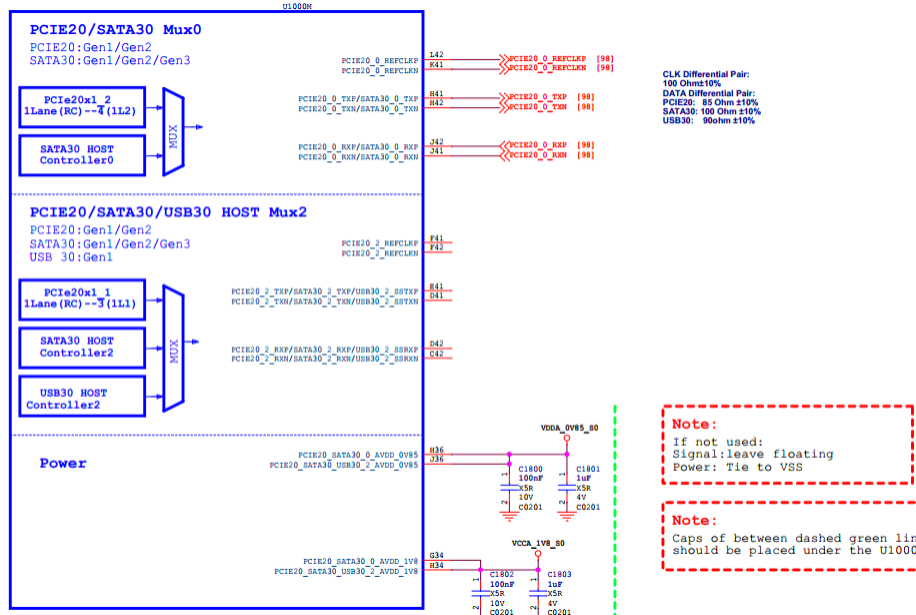

The following diagram shows RK3588 comboPHY and its possible controllers. Red boxes are controllers, pink boxes are PHY signals, green boxes are peripheral signals. Which controller is used can be confirmed by peripheral signal connections or by checking with hardware engineers. In this diagram, Mux0's PHY (combphy0_ps) is in SATA mode, not PCIe; Mux1's PHY (combphy1_ps) works with PCIe30x1_0 (dts name pcie2x1l0) and may be in PCIe mode, depending on the connected device; Mux2's PHY (combphy2_psu) works with PCIe30x1_1 (dts name pcie2x1l1) in PCIe mode to connect a PCIe NIC.

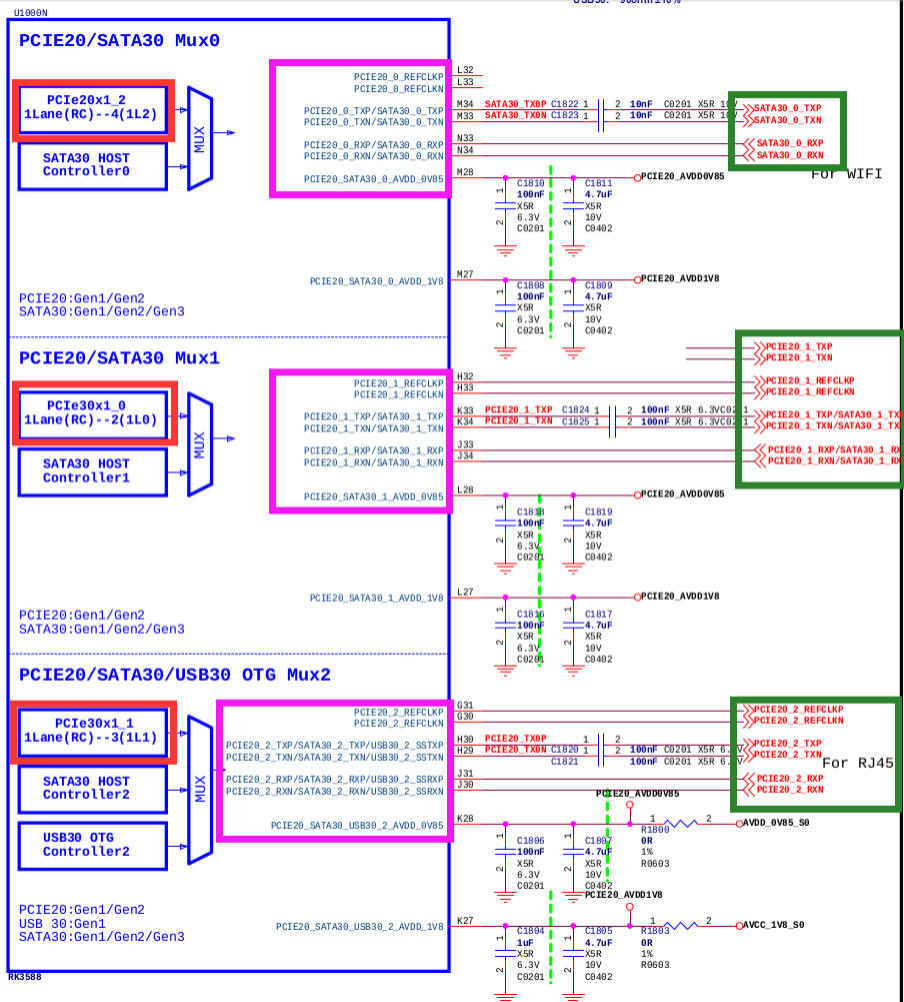

The following diagram shows the PCIe3.0 interface power supply on RK3588 evb1. You can locate the corresponding RK3588 GPIO by the PCIE30X4_PWREN_H signal, then fill it in the pcie3x4 controller dts.

2.8 Wi-Fi module device tree example

Since Wi-Fi modules are usually connected to PCIe2.0 ports, and their use of

combphyis complex, with different power, suspend, and reset requirements from other devices, here is a device tree example for reference.- Check the schematic to determine which combphy the Wi-Fi module uses. The combphy node number indicates the Mux relationship, and the suffix indicates the multiplexing: p, s, u, q represent PCIe, SATA, USB, QSGMII. In this example, Wi-Fi is connected to the PCIe/SATA muxed

PCIE20/SATA30 Mux0, so configure the combphy0_ps node.

- Search the dts file to ensure other controllers sharing this combphy are disabled to prevent signal interference.

- Move the wifi_reg_on signal from the wireless_wlan node to the PCIe 3.3v power control node.

- If Wi-Fi needs L1.x power mode, see the "RC mode PM L1 Substates support" section.

- If Wi-Fi needs wireless wakeup, ensure wifi_reg_on pin stays high during suspend, and wifi_host_wake pin is connected to a non-power-off PMU IO to generate an interrupt to wake the host. For hardware and software details, see the relevant chapters in our SDK documentation "Rockchip_Developer_Guide_Linux_WIFI_BT_CN.pdf".

- rockchip,enable-ssc

-

+ vcc3v3_pcie20_wifi: vcc3v3-pcie20-wifi {

+ compatible = "regulator-fixed";

+ regulator-name = "vcc3v3_pcie20_wifi";

+ regulator-min-microvolt = <3300000>;

+ regulator-max-microvolt = <3300000>;

+ enable-active-high;

+ /*

+ * wifi_reg_on is enabled after vbat and vddio are stable, and pulled high before reset-gpios,

+ * so putting it in the PCIe power node meets the module timing, referencing wifi_poweren_gpio.

+ */

+ pinctrl-0 = <&wifi_poweren_gpio>;

+ startup-delay-us = <5000>;

+ vin-supply = <&vcc12v_dcin>;

+ };

wireless_wlan: wireless-wlan {

compatible = "wlan-platdata";

wifi_chip_type = "ap6275p";

pinctrl-names = "default";

pinctrl-0 = <&wifi_host_wake_irq>;

WIFI,host_wake_irq = <&gpio0 RK_PA0 GPIO_ACTIVE_HIGH>;

+ /* Note: wifi_reg_on pin also needs to be configured here for WiFi driver control */

+ WIFI,poweren_gpio = <&gpio0 RK_PC7 GPIO_ACTIVE_HIGH>;

status = "okay";

};

+

+&sata0 {

+ status = "disabled" /* sata0 shares combphy0_ps with pcie2x1l2, must be disabled */

+}

+

+&combphy0_ps {

+ status = "okay"; /* Ensure phy is enabled */

+};

+

+&pcie2x1l2 {

+ reset-gpios = <&gpio3 RK_PD1 GPIO_ACTIVE_HIGH>;

+ rockchip,skip-scan-in-resume;

+ rockchip,perst-inactive-ms = <500>; /* Refer to Wi-Fi module manual for required #PERST reset time */

+ vpcie3v3-supply = <&vcc3v3_pcie20_wifi>;

+ status = "okay";

+};

&pinctrl {

wireless-wlan {

wifi_poweren_gpio: wifi-poweren-gpio {

+ //PCIE REG ON: Must be configured as pull-up

+ rockchip,pins = <0 RK_PC7 RK_FUNC_GPIO &pcfg_pull_up>;

};

};

};

3. menuconfig configuration

- Make sure the following configs are enabled to use PCIe features correctly

CONFIG_PCI=y

CONFIG_PCI_DOMAINS=y

CONFIG_PCI_DOMAINS_GENERIC=y

CONFIG_PCI_SYSCALL=y

CONFIG_PCI_BUS_ADDR_T_64BIT=y

CONFIG_PCI_MSI=y

CONFIG_PCI_MSI_IRQ_DOMAIN=y

CONFIG_PHY_ROCKCHIP_SNPS_PCIE3=y

CONFIG_PHY_ROCKCHIP_NANENG_COMBO_PHY=y

CONFIG_PCIE_DW=y

CONFIG_PCIE_DW_HOST=y

CONFIG_PCIE_DW_ROCKCHIP=y

CONFIG_PCIEPORTBUS=y

CONFIG_PCIE_PME=y

CONFIG_GENERIC_MSI_IRQ=y

CONFIG_GENERIC_MSI_IRQ_DOMAIN=y

CONFIG_IRQ_DOMAIN=y

CONFIG_IRQ_DOMAIN_HIERARCHY=y

- Enable NVMe devices (PCIe SSDs), PCIe-to-AHCI devices (SATA), PCIe-to-USB devices (XHCI) are enabled by default config, please confirm. For other devices such as Ethernet cards, WiFi, please check the relevant config yourself.

CONFIG_BLK_DEV_NVME=y

CONFIG_SATA_PMP=y

CONFIG_SATA_AHCI=y

CONFIG_SATA_AHCI_PLATFORM=y

CONFIG_ATA_SFF=y

CONFIG_ATA=y

CONFIG_USB_XHCI_PCI=y

CONFIG_USB_XHCI_HCD=y

Note: The default kernel only supports PCIe-to-SATA devices listed in drivers/ata/ahci.c. For others, please contact the manufacturer or agent for support.

4. Standard EP function development

Some Rockchip chips' PCIe controllers support EP mode, allowing the chip to be developed as a standard PCIe EP product. For EP function implementation, see the document "Rockchip_Developer_Guide_PCIE_EP_Stardard_Card_CN".

5. RC mode PM L1 Substates Support

When it is confirmed that both the RK host controller and the connected peripherals support PCIe PM L1 Substates, you can enable the PM L1 Substates feature to further optimize power consumption.

It is further emphasized that if there are devices in the target peripherals that do not support PM L1 Substates, especially if the motherboard is designed for slot external non-fixed devices, do not enable the PM L1 Substates feature, otherwise some devices may not work properly.

Hardware Circuit Design Supporting PM L1 Substates

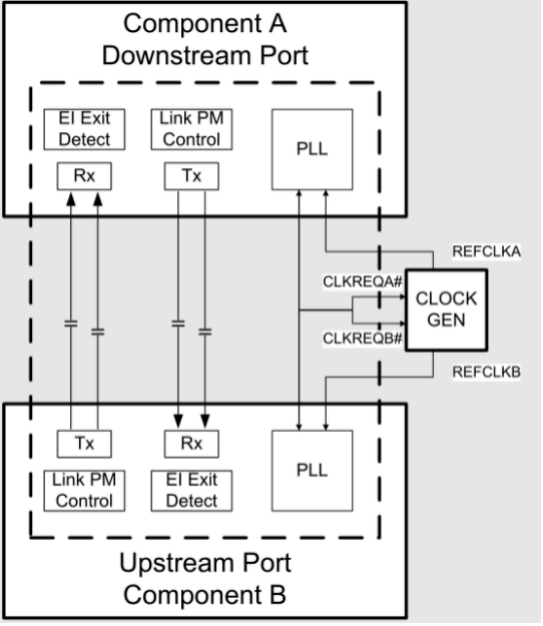

RC CLKREQ#, EP CLKREQ# are interconnected at both ends.

Optional optimization: For the external reference clock scheme, you can consider connecting CLKREQ# to CLOCK_GEN OE. If CLOCK_GEN OE is active high, an inverter should be added.

System Default Settings

System support for PM L1 Substates is disabled:

- The dts does not add the

supports-clkreq;property - Kernel macro configuration

CONFIG_PCIEASPM_POWER_SUPERSAVE=n

Enabling PM L1 Substates Support in the System

- Confirm that both RC/EP support PM L1 Substates. For RC support, refer to the "Chip Resource Introduction" chapter under the ASPM section.

- Hardware configuration of the CLKREQ# signal: Ensure compliance with the "Hardware Circuit Design Supporting PM L1 Substates"

- Software configuration of the CLKREQ# signal: Set the CLKREQ# iomux to function io

- Add the

supports-clkreq;property to the controller node in the software configuration. For details, refer to "dts Configurable Item 11" - Enable PM L1 Substates support:

- Method 1: Kernel macro configuration

CONFIG_PCIEASPM_POWER_SUPERSAVE=y - Method 2: Some peripherals such as WIFI support enabling PM L1 Substates in the driver

- Method 1: Kernel macro configuration

Note:

- If you try to enable the kernel macro configuration without strictly meeting the above conditions, the PCIe link may enter an abnormal state and fail to wake up.

- Please ensure that the kernel source code is up-to-date and includes the L1SS support patch: commit e18dfa93 PCI: rockchip: dw: Support PM L1 clock removing

6. GPIO-based Hotplug Detection Mechanism

6.1 Hardware Requirements

- The PRSNT#_1 of the PCIe slot needs to be connected to any GPIO of the host controller as a detection pin.

- The power supply of the PCIe device needs to be software-controllable for power on/off.

6.2 Software Requirements

- At least include the following commits. If not, please contact the business for patches:

commit 4de1a0c19e0f9804ba22e7f5e544fea317913957

Author: Shawn Lin <shawn.lin@rock-chips.com>

Date: Tue Mar 12 16:38:46 2024 +0800

PCI: rockchip: dw: Add gpio based hotplug

Change-Id: I49c57755d11cc43bbf7cf9eb23542f5e1e11aaa3

commit 86f3010d7f523c9f5a2e88d9f8f1871ed89da098

Author: Vidya Sagar <vidyas@nvidia.com>

Date: Sat Oct 1 00:57:45 2022 +0530

FROMLIST: PCI/hotplug: Add GPIO PCIe hotplug driver

Change-Id: Iafa798ee4d98f195f5d33d80120da0c569132548

- The kernel must confirm the following configurations are enabled:

CONFIG_HOTPLUG_PCI=y

CONFIG_HOTPLUG_PCI_GPIO=y

- DTS configuration reference:

&pcie0 {

reset-gpios = <&gpio4 RK_PC7 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie0>;

hotplug-gpios = <&gpio4 RK_PC4 IRQ_TYPE_EDGE_BOTH>;

pinctrl-names = "default";

pinctrl-0 = <&hot_plug0>;

status = "okay";

};

&pinctrl {

pcie {

hot_plug0: hot-plug0 {

rockchip,pins = <4 RK_PC4 RK_FUNC_GPIO &pcfg_pull_up>;

};

};

};

6.3 Usage Restrictions

- Hot-plugging PCIe devices while powered can easily damage the device and the host controller. The device removal and power-off process takes some time after device removal, so rapid hot-plugging is prohibited. You need to wait until the following removal log appears before reinserting:

[ 35.680289][ T134] pcieport 0000:00:00.0: Hot-UnPlug Event

[ 35.680361][ T134] pcieport 0000:00:00.0: Power Status = 1

[ 35.827183][ T134] rk-pcie 2a200000.pcie: rk_pcie_slot_disable

[ 35.827303][ T134] pcieport 0000:00:00.0: Hot-UnPlug Event

[ 35.827323][ T134] pcieport 0000:00:00.0: Power Status = 0

[ 35.827334][ T134] pcieport 0000:00:00.0: Device is already removed

-

To ensure data integrity and system stability, make sure the system stops accessing the device to be removed.

-

It is not possible to support individual hot-plugging of downstream devices under a switch. If this is required, first confirm that the switch supports individual hot-plugging of downstream devices, then refer to the "How to rescan or replace a single downstream device online?" section in common application issues for rescan processing, which can achieve the same effect.

-

Detection of device insertion or removal is not supported in suspend or standby states.

7. Kernel DMATEST

Before development, please confirm whether the target PCIe controller supports DMA transfer. For details, refer to the "Chip Resource Introduction" chapter.

RK PCIe DMA provides a test mechanism based on the kernel module_param mechanism, similar to Linux dmatest. You can further complete PCIe DMA applications under the kernel based on this framework.

Kernel Version Requirements

At least include the following commit. If not, please contact the business for patches:

commit a7c40cb119703e566d9d5befb8c1a7b0533dd7b7

Author: Jon Lin <jon.lin@rock-chips.com>

Date: Tue Jan 17 17:46:48 2023 +0800

PCI: rockchip: dw-dmatest: Suppport rc dma

1.Set rc dma as default

2.Changet to ep dma by sending command:

echo 0 > ./sys/module/pcie_dw_dmatest/parameters/is_rc

Change-Id: I9b16c328c08f220772e487c7c796b8898d74ae10

Signed-off-by: Jon Lin <jon.lin@rock-chips.com>

Test Macro Configuration

CONFIG_PCIE_DW_DMATEST=y

CONFIG_ROCKCHIP_PCIE_DMA_OBJ=n

Setup Environment

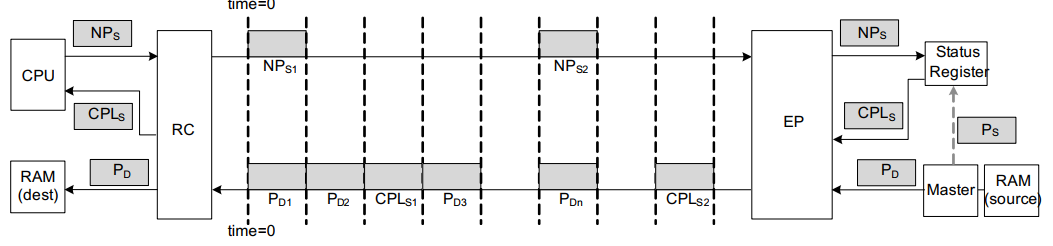

PCIe interconnection model:

- Customers can build their own RK RC - FPGA EP environment

- RK local test setup: RK RC (RK dmatest configuration) - RK EP (RK chip interconnection configuration)

Note:

- MPS is configured as 256B

- Both RC and EP need reserved memory. It is recommended to reserve 64MB of test memory at 0x3c000000 (default test address)

- It is recommended to disable other unrelated PCIe controllers

Test

For details, refer to the pcie-dw-misc-dmatest.c source code

static int size = 0x20;

module_param(size, int, 0644);

MODULE_PARM_DESC(size, "each packet size in bytes");

static unsigned int cycles_count = 1;

module_param(cycles_count, uint, 0644);

MODULE_PARM_DESC(cycles_count, "how many erase cycles to do (default 1)");

static bool irq;

module_param(irq, bool, 0644);

MODULE_PARM_DESC(irq, "Using irq? (default: false)");

static unsigned int chn_en = 1;

module_param(chn_en, uint, 0644);

MODULE_PARM_DESC(chn_en, "Each bits for one dma channel, up to 2 channels, (default enable chanel 0)");

static unsigned int rw_test = 3;

module_param(rw_test, uint, 0644);

MODULE_PARM_DESC(rw_test, "Read/Write test, 1-read 2-write 3-both(default 3)");

static unsigned int bus_addr = 0x3c000000;

module_param(bus_addr, uint, 0644);

MODULE_PARM_DESC(bus_addr, "Dmatest chn0 bus_addr(remote), chn1 add offset 0x100000, (default 0x3c000000)");

static unsigned int local_addr = 0x3c000000;

module_param(local_addr, uint, 0644);

MODULE_PARM_DESC(local_addr, "Dmatest chn0 local_addr(local), chn1 add offset 0x100000, (default 0x3c000000)");

static unsigned int test_dev;

module_param(test_dev, uint, 0644);

MODULE_PARM_DESC(test_dev, "Choose dma_obj device,(default 0)");

static bool is_rc = true;

module_param_named(is_rc, is_rc, bool, 0644);

MODULE_PARM_DESC(is_rc, "Test port is rc(default true)");

Example 1: RC device, channel 0, write data, data size 1MB, 1000 cycles, local address 0x3c000000, remote address 0x3c000000:

echo 0 > ./sys/module/pcie_dw_dmatest/parameters/test_dev

echo 1 > ./sys/module/pcie_dw_dmatest/parameters/is_rc

echo 1 > ./sys/module/pcie_dw_dmatest/parameters/chn_en

echo 1 > ./sys/module/pcie_dw_dmatest/parameters/rw_test

echo 0x100000 > ./sys/module/pcie_dw_dmatest/parameters/size

echo 1000 > ./sys/module/pcie_dw_dmatest/parameters/cycles_count

echo 0x3c000000 > ./sys/module/pcie_dw_dmatest/parameters/local_addr

echo 0x3c000000 > ./sys/module/pcie_dw_dmatest/parameters/bus_addr

echo run > ./sys/module/pcie_dw_dmatest/parameters/dmatest

Example 2: EP device, channel 0/1 (dual threads running simultaneously), read and write data, data size 8KB, 10000 cycles, local address 0x3c000000, remote address 0x3c000000:

echo 0 > ./sys/module/pcie_dw_dmatest/parameters/test_dev

echo 0 > ./sys/module/pcie_dw_dmatest/parameters/is_rc

echo 3 > ./sys/module/pcie_dw_dmatest/parameters/chn_en

echo 3 > ./sys/module/pcie_dw_dmatest/parameters/rw_test

echo 0x2000 > ./sys/module/pcie_dw_dmatest/parameters/size

echo 10000 > ./sys/module/pcie_dw_dmatest/parameters/cycles_count

echo 0x3c000000 > ./sys/module/pcie_dw_dmatest/parameters/local_addr

echo 0x3c000000 > ./sys/module/pcie_dw_dmatest/parameters/bus_addr

echo run > ./sys/module/pcie_dw_dmatest/parameters/dmatest

8. Kernel Stability Statistics Information

If the PCIe device exhibits abnormal behavior during long-term operation and its running state does not meet expectations, you can try to obtain information from the debugfs node for analysis. To enable this feature, make sure the following commit is included (pcie: rockchip: dw: Add debugfs support), otherwise you can obtain 0001-pcie-rockchip-dw-Add-debugfs-support.patch from the Redmine system as shown in the appendix.

Usage

- Identify the controller address node where the problematic device is located. You can check it from the boot enumeration log or directly from the dtsi.

- Take fe16000.pcie as an example, enter the

/sys/kernel/debug/fe160000.pciedirectory. echo disable > err_eventto disable all event statistics functions.echo clear > err_eventto clear all event statistics counters.echo enable > err_eventto enable all event statistics functions.- Start device aging and reproduce your abnormal case. After reproduction, execute

cat dumpfifoandcat err_event. - Compare the exported information with the Debugfs export information analysis table in the appendix of this document to roughly identify the problem.

9. Kernel Error Injection Test Support

If you need to test the RC-side function driver, business model/EP-side firmware/dual-end hardware IP fault tolerance for PCIe link, you can enable error injection testing to simulate possible error types during interaction and evaluate the stability of dual-end software and IP.

Usage

(1) The following commit is required:

commit fe835d5fd3329ba629f8c4290c818ef4b8f9895d

Author: Shawn Lin <shawn.lin@rock-chips.com>

Date: Wed Sep 4 17:04:37 2024 +0800

PCI: rockchip: dw: Add fault injection support

Change-Id: Ib214cc1be565bf16bafb6a847215572f35c43753

(2) The feature described in the "Kernel Stability Statistics Information" section of this document must be enabled, and enter the corresponding controller directory.

(3) echo "einj_number enable_or_disable error_type error_number" >

fault_injection

|-------------------|--------------------------------------------------------

--|

| Value | Meaning

|

|-------------------|--------------------------------------------------------

--|

|einj_number: |Error injection group number, only supports 0 to 6, other values are invalid

|

|-------------------|--------------------------------------------------------

--|

|enable_or_disable: |Enable or disable error injection, 0 means disable, 1 means enable, other values are invalid

|

|-------------------|--------------------------------------------------------

--|

|error_type: |Error injection type selection, select the error type corresponding to the group number according to the appendix|

|-------------------|--------------------------------------------------------

--|

|error_number: |Number of error injections, only supports 0 to 255, other values are invalid

|

|-------------------|--------------------------------------------------------

--|

For example, echo "2 1 2 128" > fault_injection means to enable einj2 and inject 128 NAK DLLP packets.

(4) Start PCIe link transmission, for example NVMe: dd if=/dev/nvme0n1 of=/dev/null bs=1M count=5000

(5) Check if the error occurred: cat err_event

Rx Recovery Request: 0x1f

...

Tx Nak DLLP: 0x80

(6) Analyze the dual-end software and hardware to see if unexpected software or hardware exceptions occur.

10. Kernel PMU perf Support

10.1 Software and Configuration

(1) The following five commits are required:

commit 0270f32f207f5682a729c17e977eb87bba83823e

Author: Shuai Xue <xueshuai@linux.alibaba.com>

Date: Fri Dec 8 10:56:50 2023 +0800

UPSTREAM: PCI: Move pci_clear_and_set_dword() helper to PCI header

Change-Id: I35125190a4dd8ba25e6ec14b4712750605c22285

commit 1b627c690ade9a72e3cd488e2e11edffb5d0e879

Author: Shuai Xue <xueshuai@linux.alibaba.com>

Date: Fri Dec 8 10:56:49 2023 +0800

UPSTREAM: PCI: Add Alibaba Vendor ID to linux/pci_ids.h

Change-Id: I86188f119a42548ab777df0449f7d0a933f34d12

commit dcfa6c8947baeac74ab44ea8f03d3831a062c14b

Author: Shuai Xue <xueshuai@linux.alibaba.com>

Date: Fri Dec 8 10:56:51 2023 +0800

BACKPORT: drivers/perf: add DesignWare PCIe PMU driver

Change-Id: I470f4dc2791168760517c77dd31a4dacd7dab591

commit 6cb6a00862fa29f815412634569e2015f86e397a

Author: Shawn Lin <shawn.lin@rock-chips.com>

Date: Tue Sep 3 16:24:36 2024 +0800

perf/dwc_pcie: Add support for Rockchip vendor devices

Change-Id: I6fde80440d2fa058b38a7d927eb846f477812b5f

commit 50cb3fcd18fb9defe23ba95eb3962a287e957166

Author: Shawn Lin <shawn.lin@rock-chips.com>

Date: Tue Sep 3 16:24:36 2024 +0800

PCI: rockchip: dw: Add dwc pmu support for rockchip

Change-Id: Ia27ee055aa3e63deeb7fd646411c3542b7019288

(2) The kernel needs to enable the CONFIG_PERF_EVENTS configuration.

(3) The system needs to integrate the perf tool; if not, you can download it from the development resources address mentioned in the appendix of this document.

10.2 Usage Instructions

(1) List all configurations supported by DWC PCIe PMU

root@rk3576-buildroot:/# /userdata/perf list | grep dwc_rootport

dwc_rootport_0/CFG_RCVRY/ [Kernel PMU event] # Link rcvry time ratio

dwc_rootport_0/L0/ [Kernel PMU event] # Link in L0 ratio

dwc_rootport_0/L1/ [Kernel PMU event] # Link in L1 ratio

dwc_rootport_0/L1_1/ [Kernel PMU event] # Link in L1.1 ratio

dwc_rootport_0/L1_2/ [Kernel PMU event] # Link in L1.2 ratio

dwc_rootport_0/L1_AUX/ [Kernel PMU event] # RK does not support this state

dwc_rootport_0/RX_L0S/ [Kernel PMU event] # RX in L0s ratio

dwc_rootport_0/Rx_CCIX_TLP_Data_Payload/ [Kernel PMU event] # RK does not support CCI data statistics

dwc_rootport_0/Rx_PCIe_TLP_Data_Payload/ [Kernel PMU event] # RX TLP data volume

dwc_rootport_0/TX_L0S/ [Kernel PMU event] # TX in L0s ratio

dwc_rootport_0/TX_RX_L0S/ [Kernel PMU event] # TX/RX both in L0s ratio

dwc_rootport_0/Tx_CCIX_TLP_Data_Payload/ [Kernel PMU event] # RK does not support CCI data statistics

dwc_rootport_0/Tx_PCIe_TLP_Data_Payload/ [Kernel PMU event] # TX TLP data volume

dwc_rootport_0/one_cycle/ [Kernel PMU event] # RK does not support

dwc_rootport_0/rx_ack_dllp,lane=?/ [Kernel PMU event] # Number of RX replied DLLP

dwc_rootport_0/rx_atomic,lane=?/ [Kernel PMU event] # RK does not support

dwc_rootport_0/rx_ccix_tlp,lane=?/ [Kernel PMU event] # RK does not support

dwc_rootport_0/rx_completion_with_data,lane=?/ [Kernel PMU event] # RX cplt packets with data

dwc_rootport_0/rx_completion_without_data,lane=?/ [Kernel PMU event] # RX cplt packets without data

dwc_rootport_0/rx_duplicate_tl,lane=?/ [Kernel PMU event] # RX/TL dup error count

dwc_rootport_0/rx_io_read,lane=?/ [Kernel PMU event] # RX ior packet count

dwc_rootport_0/rx_io_write,lane=?/ [Kernel PMU event] # RX iow packet count

dwc_rootport_0/rx_memory_read,lane=?/ [Kernel PMU event] # RX memr packet count

dwc_rootport_0/rx_memory_write,lane=?/ � [Kernel PMU event] # RX memw packet count

dwc_rootport_0/rx_message_tlp,lane=?/ [Kernel PMU event] # RX received msg count

dwc_rootport_0/rx_nulified_tlp,lane=?/ [Kernel PMU event] # RX TLPs discarded due to errors

dwc_rootport_0/rx_tlp_with_prefix,lane=?/ [Kernel PMU event] # RX TLPs with prefix

dwc_rootport_0/rx_update_fc_dllp,lane=?/ [Kernel PMU event] # RX received flow control packets

dwc_rootport_0/tx_ack_dllp,lane=?/ [Kernel PMU event] # TX replied DLLP count

dwc_rootport_0/tx_atomic,lane=?/ [Kernel PMU event] # RK does not support

dwc_rootport_0/tx_ccix_tlp,lane=?/ [Kernel PMU event] # RK does not support

dwc_rootport_0/tx_completion_with_data,lane=?/ [Kernel PMU event] # TX cplt packets with data

dwc_rootport_0/tx_completion_without_data,lane=?/ [Kernel PMU event] # TX cplt packets without data

dwc_rootport_0/tx_configuration_read,lane=?/ [Kernel PMU event] # TX cfg-r packet count

dwc_rootport_0/tx_configuration_write,lane=?/ [Kernel PMU event] # TX cfg-w packet count

dwc_rootport_0/tx_io_read,lane=?/ [Kernel PMU event] # TX ior packet count

dwc_rootport_0/tx_io_write,lane=?/ [Kernel PMU event] # TX iow packet count

dwc_rootport_0/tx_memory_read,lane=?/ [Kernel PMU event] # TX memr packet count

dwc_rootport_0/tx_memory_write,lane=?/ [Kernel PMU event] # TX memw packet count

dwc_rootport_0/tx_message_tlp,lane=?/ [Kernel PMU event] # TX received msg count

dwc_rootport_0/tx_nulified_tlp,lane=?/ [Kernel PMU event] # TX TLPs discarded due to errors

dwc_rootport_0/tx_tlp_with_prefix,lane=?/ [Kernel PMU event] # TX sent TLPs with prefix

dwc_rootport_0/tx_update_fc_dllp,lane=?/ [Kernel PMU event] # TX sent flow control packets

(2) Start a perf function, for example, to count RX TLP based on time:

/userdata/perf stat -a -e dwc_rootport_0/Rx_PCIe_TLP_Data_Payload/

(3) Start transmission

root@rk3576-buildroot:/# dd if=/dev/nvme0n1 of=/dev/null bs=1M count=5000

dd if=/dev/nvme0n1 of=/dev/null bs=1M count=5000

5000+0 records in

5000+0 records out

5242880000 bytes (5.2 GB, 4.9 GiB) copied, 14.9016 s, 352 MB/s

(4) View statistics

Performance counter stats for 'system wide':

5221423060 dwc_rootport_0/Rx_PCIe_TLP_Data_Payload/ (50.01%)

28.298528222 seconds time elapsed

(5) Similarly, you can test the amount of TX TLP data, then calculate the average RX/TX bandwidth:

PCIe RX Bandwidth = Rx_PCIe_TLP_Data_Payload / statistics duration

PCIe TX Bandwidth = Tx_PCIe_TLP_Data_Payload / statistics duration

(6) Lane event statistics

Since each Lane has the same events, to avoid generating a lot of redundant information, it is recommended to specify the Lane ID, for example:

/userdata/perf stat -a -e dwc_rootport_0/rx_memory_read,lane=1/

11. Common Application Issues

11.1 Can different lanes be interleaved if the routing position is not ideal?

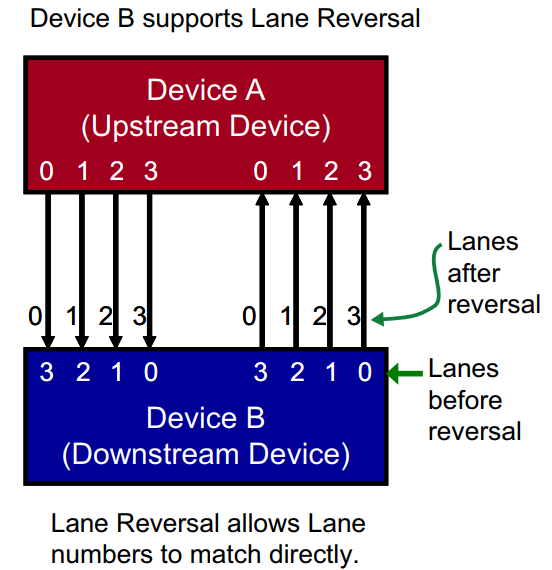

- Lane reversal is supported, which is a hardware protocol behavior and does not require software changes. However, there are the following restrictions:

- In the case of 4 lanes, the RK platform currently only supports full reverse interleaving, that is, RC Lane[0.1.2.3] corresponds to EP Lane[3.2.1.0] respectively, and other cases are not supported.

- In the case of 2 lanes, similarly, RC Lane[0.1] corresponds to EP Lane[1.0].

It is not supported to combine signals between different groups of lanes on the same side, such as combining RC lane0 TX and lane1 RX as a group of lanes to connect external devices.

11.2 Can the differential signals of the same lane be interleaved?

PN inversion (Lane polarity) is supported. Normally, RC TX+ connects to EP RX+, RC TX- connects to EP RX-, and RC TX+ connects to EP RX- and other PN inversion wiring are supported. No additional software processing is required, and the PCIe controller automatically detects it.

TX/RX interleaving is not supported, for example, RC lane1 TX cannot be connected to EP lane1 TX.

11.3 Does the same PCIe interface support splitting or merging?

Some PCIe ports of RK chips support splitting and merging functions. Please refer to the "Chip Resource Introduction" section, and refer to the example and dts instructions for specific methods.

11.4 What clock input modes are supported by the PCIe 3.0 interface?

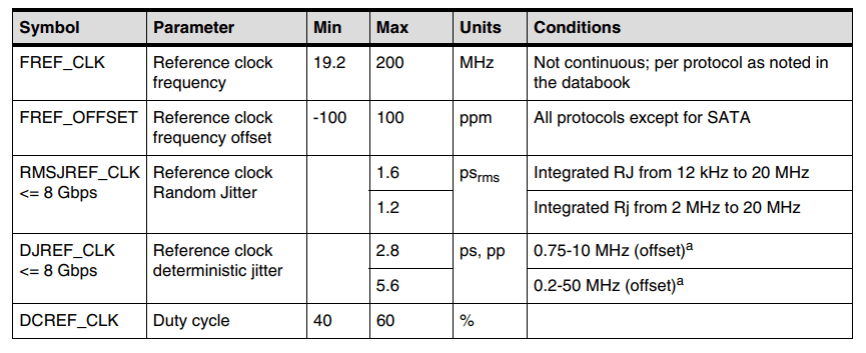

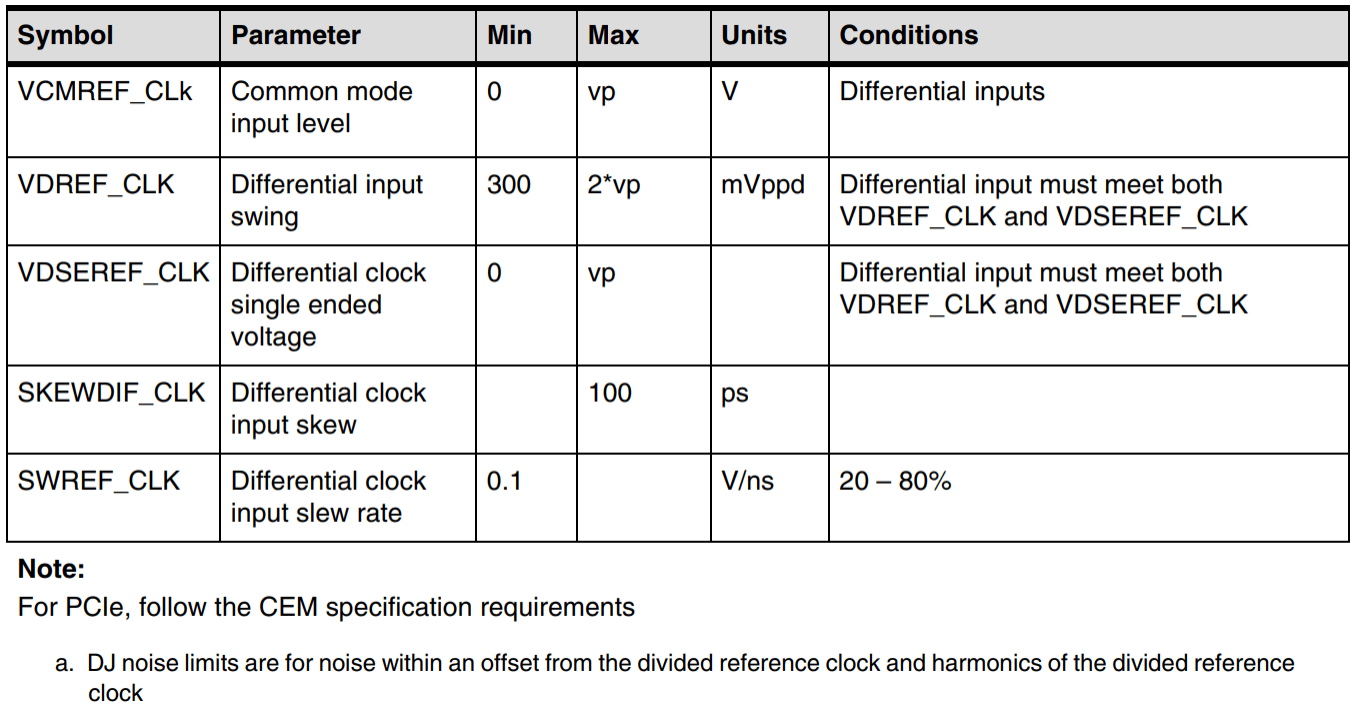

The input clock mode of PCIe 3.0 PHY can be HCSL, LPHCSL, or other differential signals, such as input clock schemes implemented by supporting LVDS plus level conversion circuits, etc. All of the above are subject to meeting PHY indicators.

11.5 Is PCIe switch supported? Do you have any recommendations?

Theoretically supported, no patches are required, and there is no recommended list. To control risks, please contact the supplier to borrow an evaluation board, insert it into our EVB for verification before purchasing.

11.6 How to determine the correspondence between controllers and devices in the system?

Take the RK3568 chip as an example:

| Controller | Bus Address Range |

|---|---|

| PCIe2x1 Controller | 0x00~0x0f |

| PCIe3x1 Controller | 0x10~0x1f |

| PCIe3x2 Controller | 0x20~0x2f |

From the output of lspci, you can see the bus address (high bits) assigned to each device, and thus determine the correspondence. The second column "Class" is the device type, and the third column is VID:PID.

console:/ # lspci

21:00.0 Class 0108: 144d:a808

20:00.0 Class 0604: 1d87:3566

11:00.0 Class 0c03: 1912:0014

10:00.0 Class 0604: 1d87:3566

01:00.0 Class 0c03: 1912:0014

00:00.0 Class 0604: 1d87:3566

For Class types, please refer to https://pci-ids.ucw.cz/read/PD/, and for vendor VID and product PID, please refer to http://pci-ids.ucw.cz/v2/pci.ids.

If you need to adjust the controller's bus-range, please adjust the bus-range allocation of the three controllers in rk3568.dtsi, and be sure not to overlap. In addition, adjusting bus-range will cause the MSI(-X) RID range of the device to change, so please adjust msi-map accordingly.

bus-range = <start address end address>

msi-map = < bus-range start address << 8

&its

bus-range start address << 8

total number of buses allocated in bus-range << 8>

For example, if bus-range is adjusted to 0x30 ~ 0x60, that is, the bus address assigned to downstream devices of this controller is from 0x30 to 0x60, with a total of 0x30 buses, then msi-map can be configured as follows:

msi-map = <0x3000 &its 0x3000 0x3000>;

And so on. Be sure to ensure that the bus-range and msi-map of the three controllers do not overlap, and that bus-range and msi-map match each other.

11.17 How to trigger MSI-X interrupt from RK PCIe EP via command?

Principle

The PC configures the MSI table through the standard MSI-X cap mapped BAR4.

RK3568 Example:

# After loading the driver and configuring msix, execute the following two commands on the device side to view the MSI-X table

io -4 0xfe280270 0x10001 # Enable Dbi writeable for testing

io -4 -l 0x100 0xf6300000

io -4 0xfe280270 0x10000

f6300000: fee02004 00000000 00000024 00000000

f6300010: fee08004 00000000 00000024 00000000

f6300020: fee01004 00000000 00000024 00000000

f6300030: fee02004 00000000 00000025 00000000

f6300040: fee08004 00000000 00000025 00000000

f6300050: fee01004 00000000 00000025 00000000

f6300060: fee02004 00000000 00000026 00000000

f6300070: fee04004 00000000 00000026 00000000

f6300080: 00000000 00000000 00000000 00000001

f6300090: 00000000 00000000 00000000 00000001

f63000a0: 00000000 00000000 00000000 00000001

f63000b0: 00000000 00000000 00000000 00000001

f63000c0: 00000000 00000000 00000000 00000001

f63000d0: 00000000 00000000 00000000 00000001

f63000e0: 00000000 00000000 00000000 00000001

f63000f0: 00000000 00000000 00000000 00000001

# Since the current business does not provide an MSI-X interface example, you can trigger MSI-X as follows

# Set device outbound, by default RK EP outbound configures CPU addr as 0xf0000000, not changed during testing, or

complete Bar outbound configuration via kernel interface

io -4 0xf6300014 0xfee00000 # Points to the address output by io -4 -l 0x100 0xf5300000 above

io -4 0xf6300018 0x0

# Trigger MSI-X

io -4 0xf0002004 0x24

io -4 0xf0008004 0x24

io -4 0xf0001004 0x24

io -4 0xf0002004 0x25

io -4 0xf0008004 0x25

io -4 0xf0001004 0x25

io -4 0xf0002004 0x26

io -4 0xf0004004 0x26

RK3588 Example:

# After loading the driver and configuring msix, execute the following two commands on the device side to view the MSI-X table

io -4 0xfe150270 0x10001 # Enable Dbi writeable for testing

io -4 -l 0x100 0xf5300000

io -4 0xfe150270 0x10000

f5300000: fee02004 00000000 00000024 00000000

f5300010: fee08004 00000000 00000024 00000000

f5300020: fee01004 00000000 00000024 00000000

f5300030: fee02004 00000000 00000025 00000000

f5300040: fee08004 00000000 00000025 00000000

f5300050: fee01004 00000000 00000025 00000000

f5300060: fee02004 00000000 00000026 00000000

f5300070: fee04004 00000000 00000026 00000000

f5300080: 00000000 00000000 00000000 00000001

f5300090: 00000000 00000000 00000000 00000001

f53000a0: 00000000 00000000 00000000 00000001

f53000b0: 00000000 00000000 00000000 00000001

f53000c0: 00000000 00000000 00000000 00000001

f53000d0: 00000000 00000000 00000000 00000001

f53000e0: 00000000 00000000 00000000 00000001

f53000f0: 00000000 00000000 00000000 00000001

# Since the current business does not provide an MSI-X interface example, you can trigger MSI-X as follows

# Set device outbound, by default RK EP outbound configures CPU addr as 0xf0000000, not changed during testing, or

complete Bar outbound configuration via kernel interface

io -4 0xf5300014 0xfee00000 # Points to the address output by io -4 -l 0x100 0xf5300000 above

io -4 0xf5300018 0x0

# Trigger MSI-X

io -4 0xf0002004 0x24

io -4 0xf0008004 0x24

io -4 0xf0001004 0x24

io -4 0xf0002004 0x25

io -4 0xf0008004 0x25

io -4 0xf0001004 0x25

io -4 0xf0002004 0x26

io -4 0xf0004004 0x26

11.18 How to modify and increase 32bits-np mapping address space?

Background

PCIe mmio space is the mapping address space for CPU-initiated PCIe transfers, dedicated to physical addresses, and DRAM does not include this segment. Each PCIe controller has a dedicated mmio space, usually 32MB 32bits address space and 1GB 64bits address space.

PCIe range is the mapping between CPU access address and PCI domain virtual address. The allocation principle of PCIe range:

- Domain address and DRAM physical address cannot overlap to avoid EP-side DMA address confusion and access errors, so

- By default, the domain address is allocated in the corresponding PCIe controller mmio physical address, one-to-one with PCIe mmio space

- To extend a small amount of 32bits-np domain address space, it is recommended to use other PCIe controller mmio physical addresses

- To further expand more 32bits-np domain address space, it is recommended to reserve memory space within 4GB for further allocation

Default configuration confirmation, take RK3588 as an example:

[ 5.325570] pci_bus 0000:00: root bus resource [mem 0xf0200000-0xf0ffffff] # RC 14MB 32bits-np mem

[ 5.325577] pci_bus 0000:00: root bus resource [mem 0x900000000-0x93fffffff pref] # RC 1GB 64bits-pref mem

Problem: Default allocated 32bits-np space is insufficient

log:

[ 11.646077] pci 0000:01:00.0: reg 0x10: [mem 0x00000000-0x00ffffff 64bit] # Dev requires 26MB 32bits-np, will be aligned to 32MB

[ 11.646113] pci 0000:01:00.0: reg 0x18: [mem 0x00000000-0x007fffff 64bit]

[ 11.646150] pci 0000:01:00.0: reg 0x20: [mem 0x00000000-0x001fffff 64bit]

...

[ 11.971710] pci 0000:01:00.0: BAR 0: no space for [mem size 0x01000000 64bit]

[ 11.971713] pci 0000:01:00.0: BAR 0: failed to assign [mem size 0x01000000 64bit]

[ 11.971717] pci 0000:01:00.0: BAR 2: no space for [mem size 0x00800000 64bit]

[ 11.971720] pci 0000:01:00.0: BAR 2: failed to assign [mem size 0x00800000 64bit]

[ 11.971723] pci 0000:01:00.0: BAR 4: no space for [mem size 0x00200000 64bit]

[ 11.971726] pci 0000:01:00.0: BAR 4: failed to assign [mem size 0x00200000 64bit]

Solution Patch Reference

Refer to TRM to confirm the dedicated memory space for PCIe, then add the missing mem range resource.

Example 1: RK3588 pcie3x4 modifies the 240MB 32bits-np mapping space configuration, modify the kernel rk3588.dtsi corresponding node range attribute as:

ranges = <0x00000800 0x0 0xff000000 0x0 0xf0000000 0x0 0x100000

0x81000000 0x0 0xff100000 0x0 0xf0100000 0x0 0x100000

0x82000000 0x0 0xf0000000 0x9 0x00000000 0x0 0x0f000000

0xc3000000 0x9 0x10000000 0x9 0x10000000 0x0

0x30000000>;

Example 2: RK3588s pcie2x1l2 modifies the 240MB 32bits-np mapping space configuration, modify the kernel rk3588s.dtsi corresponding node range attribute as:

ranges = <0x00000800 0x0 0xff000000 0x0 0xf4000000 0x0 0x100000

0x81000000 0x0 0xff100000 0x0 0xf4100000 0x0 0x100000

0x82000000 0x0 0xf0000000 0xa 0x00000000 0x0 0x0f000000

0xc3000000 0xa 0x10000000 0xa 0x10000000 0x0

0x30000000>;

Example 3: RK3588 pcie2x1l0 modifies the 240MB 32bits-np mapping space configuration, modify the kernel rk3588.dtsi corresponding node range attribute as:

ranges = <0x00000800 0x0 0xff000000 0x0 0xff000000 0x0 0x100000

0x81000000 0x0 0xff100000 0x0 0xff100000 0x0 0x100000

0x82000000 0x0 0xf0000000 0x9 0x80000000 0x0 0x0f000000

0xc3000000 0x9 0x90000000 0x9 0x90000000 0x0

0x30000000>;

Example 3: RK3568 pcie3x2 modifies the 240MB 32bits-np mapping space configuration, modify the kernel rk356x.dtsi corresponding node range attribute as:

ranges = <0x00000800 0x0 0xff000000 0x0 0xf0000000 0x0 0x100000

0x81000000 0x0 0xff100000 0x0 0xf0100000 0x0 0x100000

0x82000000 0x0 0xf0000000 0x3 0x80000000 0x0 0x0f000000

0xc3000000 0x3 0x90000000 0x3 0x90000000 0x0

0x30000000>;

Example 4: Based on Example 1, add 256M mapped memory at 0x30000000 and reserve memory as required:

diff --git a/arch/arm64/boot/dts/rockchip/rk3588-evb1-lp4.dtsi

b/arch/arm64/boot/dts/rockchip/rk3588-evb1-lp4.dtsi

index a10dad37f9cf..d1b16e13c459 100644

--- a/arch/arm64/boot/dts/rockchip/rk3588-evb1-lp4.dtsi

+++ b/arch/arm64/boot/dts/rockchip/rk3588-evb1-lp4.dtsi

@@ -233,6 +233,15 @@ wireless_wlan: wireless-wlan {

WIFI,poweren_gpio = <&gpio3 RK_PB1 GPIO_ACTIVE_HIGH>;

status = "okay";

};

+

+ reserved-memory {

+ #address-cells = <2>;

+ #size-cells = <2>;

+ ranges;

+ pcie3x4_range: pcie3x4-range@30000000 {

+ reg = <0x0 0xdfe00000 0x0 0x10200000>;

+ };

+ };

};

&backlight {

diff --git a/arch/arm64/boot/dts/rockchip/rk3588.dtsi

b/arch/arm64/boot/dts/rockchip/rk3588.dtsi

index ad414c61fd38..096f16740e11 100644

--- a/arch/arm64/boot/dts/rockchip/rk3588.dtsi

+++ b/arch/arm64/boot/dts/rockchip/rk3588.dtsi

@@ -601,10 +601,11 @@ pcie3x4: pcie@fe150000 {

phys = <&pcie30phy>;

phy-names = "pcie-phy";

power-domains = <&power RK3588_PD_PCIE>;

- ranges = <0x00000800 0x0 0xf0000000 0x0 0xf0000000 0x0 0x100000

- 0x81000000 0x0 0xf0100000 0x0 0xf0100000 0x0 0x100000

- 0x82000000 0x0 0xf0200000 0x0 0xf0200000 0x0 0xe00000

- 0xc3000000 0x9 0x00000000 0x9 0x00000000 0x0

0x40000000>;

+ ranges = <0x00000800 0x0 0xdfe00000 0x0 0xf0000000 0x0 0x100000

+ 0x81000000 0x0 0xdff00000 0x0 0xf0100000 0x0 0x100000

+ 0x82000000 0x0 0xe0000000 0x9 0x00000000 0x0

0x20000000 // Extended to 512MB

+ 0xc3000000 0x9 0x20000000 0x9 0x20000000 0x0

0x20000000>;

reg = <0x0 0xfe150000 0x0 0x10000>,

<0xa 0x40000000 0x0 0x400000>;

reg-names = "pcie-apb", "pcie-dbi";

11.19 How to configure max payload size?

PCIe sends data in the form of TLP, and the max payload size (MPS) determines the maximum number of bytes that a PCIe device's TLP can transmit. The size of MPS is negotiated by both ends of the PCIe link, and the maximum payload sent by the PCIe device cannot exceed the MPS value.

The kernel provides a "[PCI] various PCI subsystem options." configuration based on dts. For details, refer to the "Documentation/admin-guide/kernel-parameters.txt" document. The relevant configurations are as follows:

pcie_bus_tune_off# Turn off MPS adjustment, use the device's own default valuepcie_bus_safe# Enable MPS adjustment, set the maximum MPS value supported by all devicespcie_bus_perf# Enable MPS adjustment, set to the maximum MPS according to parent bus and own capabilitypcie_bus_peer2peer# Enable MPS adjustment, set all devices' MPS to 128B

Note:

- The kernel default max payload size configuration mechanism is

pcie_bus_tune_off - Usually, you can consider directly adding the

pci=pcie_bus_safeproperty in dts bootargs

11.20 How to fix the enumerated device ID?

When there are multiple PCIe devices of the same type in the system, such as multiple network cards, due to the uncertain initialization order, the actual device represented by eth0 is not fixed. The same situation applies to NVMe, etc. If the user wants to fix the ID of the enumerated device, the corresponding function driver needs to be modified. The theoretical basis for the modification is that the device's bus number is fixed by DTS. The following two examples are for reference:

If RK3588 is connected to three network cards and you want to fix them in the following order:

pcie2x1l0: pcie@fe170000 => eth1

pcie2x1l2: pcie@fe190000 => eth2

pcie2x1l1: pcie@fe180000 => eth3

Check dtsi:

pcie2x1l0 node: bus-range = <0x20 0x2f> -> network card assigned bus number 0x21 -> eth1

pcie2x1l2 node: bus-range = <0x40 0x4f> -> network card assigned bus number 0x41 -> eth2

pcie2x1l1 node: bus-range = <0x30 0x3f> -> network card assigned bus number 0x31 -> eth3

Modify the corresponding function driver, and change the name registered to the network subsystem before the register_netdev function is called.

--- a/drivers/net/ethernet/realtek/r8168/r8168_n.c

+++ b/drivers/net/ethernet/realtek/r8168/r8168_n.c

@@ -25481,6 +25481,18 @@ static const struct net_device_ops rtl8168_netdev_ops =

{

};

#endif

+static void pci_bus_nr_2_id(struct pci_dev *pdev, struct net_device *ndev )

+{

+

+ dev_info(&pdev->dev, "%s pdev->bus->number = 0x%x\n",

+ __func__, pdev->bus->number);

+

+ if(pdev->bus->number == 0x21)

+ strcpy(ndev->name, "eth1");

+ if(pdev->bus->number == 0x41)

+ strcpy(ndev->name, "eth2");

+ if(pdev->bus->number == 0x31)

+ strcpy(ndev->name, "eth3");

+}

+

static int __devinit

rtl8168_init_one(struct pci_dev *pdev,

const struct pci_device_id *ent)

@@ -25624,7 +25636,7 @@ rtl8168_init_one(struct pci_dev *pdev,

rtl8168_set_eeprom_sel_low(tp);

rtl8168_get_mac_address(dev);

-

+ pci_bus_nr_2_id(pdev, dev); // The modification must be before register_netdev()

tp->fw_name = rtl_chip_fw_infos[tp->mcfg].fw_name;

Similarly, NVMe storage can be modified in a similar way

--- a/drivers/nvme/host/core.c

+++ b/drivers/nvme/host/core.c

@@ -5169,6 +5169,19 @@ static void nvme_free_ctrl(struct device *dev)

nvme_put_subsystem(subsys);

}

+static void pci_bus_nr_2_id(struct pci_dev *pdev, struct nvme_ctrl *ctrl)

+{

+ dev_info(&pdev->dev, "%s pdev->bus->number = 0x%x\n",

+ __func__, pdev->bus->number);

+

+ if(pdev->bus->number == 0x21)

+ ctrl->instance = 1; //pcie2x1l0 -> nvme1

+ if(pdev->bus->number == 0x41)

+ ctrl->instance = 2; //pcie2x1l2 -> nvme2

+ if(pdev->bus->number == 0x31)

+ ctrl->instance = 3; //pcie2x1l1 -> nvme3

+}

+

/*

* Initialize a NVMe controller structures. This needs to be called during

* earliest initialization so that we have the initialized structured around

@@ -5178,6 +5191,7 @@ int nvme_init_ctrl(struct nvme_ctrl *ctrl, struct device

*dev,

const struct nvme_ctrl_ops *ops, unsigned long quirks)

{

int ret;

+ struct pci_dev *pdev = container_of(dev, struct pci_dev, dev);

ctrl->state = NVME_CTRL_NEW;

clear_bit(NVME_CTRL_FAILFAST_EXPIRED, &ctrl->flags);

@@ -5214,6 +5228,8 @@ int nvme_init_ctrl(struct nvme_ctrl *ctrl, struct device

*dev,

goto out;

ctrl->instance = ret;

+ pci_bus_nr_2_id(pdev, ctrl);

device_initialize(&ctrl->ctrl_device);

ctrl->device = &ctrl->ctrl_device;

ctrl->device->devt = MKDEV(MAJOR(nvme_ctrl_base_chr_devt),

## 12. Troubleshooting

### 12.1 Driver Load Failure

```plaintext

[ 0.417008] rk-pcie 3c0000000.pcie: Linked as a consumer to regulator.14

[ 0.417477] rk-pcie 3c0800000.pcie: Linked as a consumer to regulator.14

[ 0.417648] rk-pcie 3c0800000.pcie: phy init failed

Cause: The corresponding phy node for this controller is not correctly enabled in the dts.

[ 0.195567] rochchip_p3phy_init: lock failed 0x6890000, check input refclk and power supply

[ 0.195585] phy phy-fe8c0000.phy.8: phy init failed --> -110

[ 0.195599] rk-pcie 3c0800000.pcie: fail to init phy, err -110

[ 0.195611] rk-pcie 3c0800000.pcie: phy init failed

Cause: The PCIe 3.0 PHY power supply or input clock is abnormal, causing the phy to not work properly.

12.2 Training Failure

The log of PCIe Link Fail keeps repeating "PCIe Linking...", and the LTSSM state machine may be different

rk-pcie 3c0000000.pcie: PCIe Linking... LTSSM is 0x0

rk-pcie 3c0000000.pcie: PCIe Linking... LTSSM is 0x0

rk-pcie 3c0000000.pcie: PCIe Linking... LTSSM is 0x0

Or "PCIe Link up" is printed, but bit16 and bit17 of the LTSSM state machine are not equal to 0x3, and the value of bit0 to bit8 is not greater than 0x11

[ 3.108325] rk-pcie fe150000.pcie: Looking up vpcie3v3-supply from device tree

[ 3.126926] rk-pcie fe150000.pcie: missing legacy IRQ resource

[ 3.126940] rk-pcie fe150000.pcie: IRQ msi not found

[ 3.126944] rk-pcie fe150000.pcie: use outband MSI support

[ 3.126947] rk-pcie fe150000.pcie: Missing *config* reg space

[ 3.126954] rk-pcie fe150000.pcie: host bridge /pcie@fe150000 ranges:

[ 3.126965] rk-pcie fe150000.pcie: err 0x00f0000000..0x00f00fffff ->

0x00f0000000

[ 3.126972] rk-pcie fe150000.pcie: IO 0x00f0100000..0x00f01fffff ->

0x00f0100000

[ 3.126979] rk-pcie fe150000.pcie: MEM 0x00f0200000..0x00f0ffffff ->

0x00f0200000

[ 3.126984] rk-pcie fe150000.pcie: MEM 0x0900000000..0x090fffffff ->

0x0900000000

[ 3.127007] rk-pcie fe150000.pcie: Missing *config* reg space

[ 3.127028] rk-pcie fe150000.pcie: invalid resource

[ 3.387304] rk-pcie fe150000.pcie: PCIe Link up, LTSSM is 0x0

If the link is truly successful, you should see a log like "PCIe Link up" and bit16 and bit17 of the LTSSM state machine are equal to 0x3, and the value of bit0 to bit8 is greater than or equal to 0x11

[ 2.410536] rk-pcie 3c0000000.pcie: PCIe Link up, LTSSM is 0x130011

Cause: Training failed, the peripheral is not in working state or the signal is abnormal. First, check whether reset-gpios is configured correctly. Second, check whether the 3V3 power supply of the peripheral is present and sufficient; some peripherals require a 12V power supply. Finally, test whether the timing of the reset signal and power supply conflicts with the device's spec. If none of these solve the problem, it is likely a signal integrity issue, and you need to provide an eye diagram and PCB to our hardware team. We also recommend that your company obtain a TX compatibility signal test report from a laboratory.

It is also recommended that customers enable RK_PCIE_DBG in pcie-dw-rockchip.c and capture a log for analysis. Note: If multiple controllers are used at the same time, please disable the controllers of unused or problem-free devices before capturing the log for easier analysis. In the captured log, you will see information like "rk-pcie 3c0000000.pcie: fifo_status = 0x144001". The last two digits of fifo_status are the ltssm state machine of the PCIe link, which can be used to determine the approximate situation of the exception. The PCIe ltssm state machine information of the chip can be found in the appendix at the end of the document.

12.3 PCIe3.0 Controller Device Initialization System Exception

[ 21.523506] rcu: INFO: rcu_preempt detected stalls on CPUs/tasks:

[ 21.523557] rcu: 1-...0: (0 ticks this GP) idle=652/1/0x4000000000000000 softirq=30/30 fqs=2097

[ 21.523579] rcu: 3-...0: (5 ticks this GP) idle=4fa/1/0x4000000000000000 softirq=35/36 fqs=2097

[ 21.523590] rcu: (detected by 2, t=6302 jiffies, g=-1151, q=98)

[ 21.523610] Task dump for CPU 1:

[ 21.523622] rk-pcie R running task 0 55 2 0x0000002a

[ 21.523640] Call trace:

[ 21.523666] __switch_to+0xe0/0x128

[ 21.523682] 0x43752cfcfe820900

[ 21.523694] Task dump for CPU 3:

[ 21.523704] kworker/u8:0 R running task 0 7 2 0x0000002a

[ 21.523737] Workqueue: events_unbound enable_ptr_key_workfn

[ 21.523751] Call trace:

[ 21.523767] __switch_to+0xe0/0x128

[ 21.523786] event_xdp_redirect+0x8/0x90

[ 21.523816] rcu: INFO: rcu_sched detected stalls on CPUs/tasks:

[ 21.523840] rcu: 1-...0: (50 ticks this GP) idle=652/1/0x4000000000000000 softirq=7/30 fqs=2099

[ 21.523859] rcu: 3-...0: (55 ticks this GP) idle=4fa/1/0x4000000000000000 softirq=5/36 fqs=2099

[ 21.523870] rcu: (detected by 2, t=6302 jiffies, g=-1183, q=1)

[ 21.523887] Task dump for CPU 1:

[ 21.523898] rk-pcie R running task 0 55 2 0x0000002a

[ 21.523915] Call trace:

[ 21.523931] __switch_to+0xe0/0x128

[ 21.523944] 0x43752cfcfe820900

[ 21.523955] Task dump for CPU 3:

[ 21.523965] kworker/u8:0 R running task 0 7 2 0x0000002a

[ 21.523990] Workqueue: events_unbound enable_ptr_key_workfn

[ 21.524004] Call trace:

Cause: If the system is stuck near this log, it means that the PCIe3.0 PHY is not working properly. Please check in order:

- Whether the clock input of the external crystal oscillator chip is abnormal. If there is no clock or the amplitude is abnormal, the phy will not be able to lock.

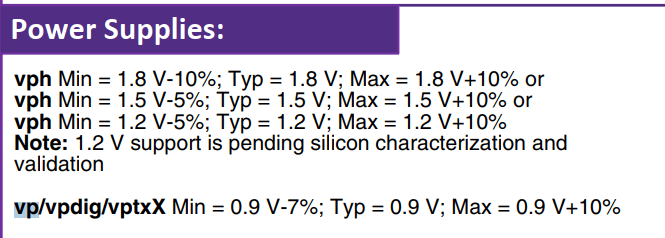

- Check whether the voltages of

PCIE30_AVDD_0V9andPCIE30_AVDD_1V8meet the requirements. - Check whether the low-speed IO of PCIe is configured in the board-level DTS. If so, please delete and test again; and refer to the "Low-speed IO Description" section for the specific usage of these IOs.

- For RK3588 pcie30phy, if only one port is used, the other port also needs to be powered. Check whether this meets the requirements.

12.4 PCIe2.0 Controller Device Initialization System Exception

[ 21.523870] rcu: (detected by 2, t=6302 jiffies, g=-1183, q=1)